AR2SEC: RISC-V Architectures for Critical Sectors

GTD leads the AR2SEC project to develop innovative, safe, and reusable RISC-V-based hardware and software systems for critical sectors like avionics, robotics, and automotive—funded by CDTI and supported by the EU NextGenerationEU plan.

Safe and Scalable Processing

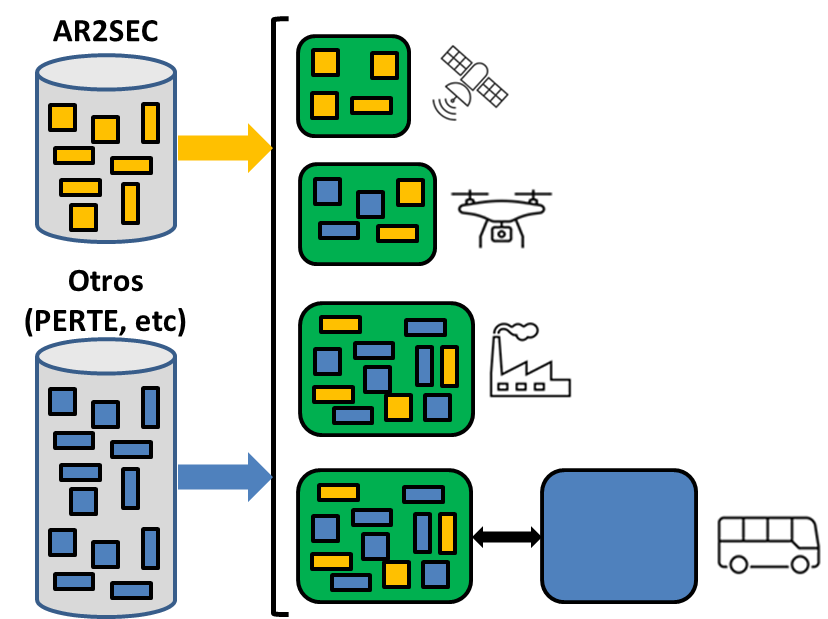

AR2SEC (High-Performance Architectures for Critical Sectors) is a cutting-edge Spanish research and development project that aims to revolutionize how computing platforms are designed for safety-critical applications. Funded under the "Programa Misiones de Ciencia e Innovación" and aligned with the PERTE Chip initiative, AR2SEC aims to design, build, and validate a new generation of high-reliability, high-performance processors and software ecosystems.

Led by GTD Science Infrastructures & Robotics, AR2SEC brings together a high-level consortium: Clue Technologies (aerospace sector lead), FENT Innovative Software Solutions, TECHNICA Electronics, and two prominent research institutions — the Barcelona Supercomputing Center (BSC) and the Center for Industrial Electronics at UPM.

.png)

Objectives

AR2SEC’s mission is to create a flexible, scalable hardware and software platform that meets the stringent safety and performance requirements of industries such as:

- Automotive

- Aerospace and Avionics

- Energy (Fusion technologies)

These industries demand computing systems that can guarantee functional safety, withstand harsh environments, and deliver real-time performance, especially as they increasingly integrate AI and Deep Learning algorithms.

To address this challenge, AR2SEC focuses on:

- Designing a customizable chip architecture based on the open RISC-V instruction set.

- Creating a robust Safety Island SoC (SISoC) that can operate either alone or alongside high-performance multi-core processors.

- Developing an ecosystem of low-level software tools including hypervisors, real-time operating systems, simulators, and verification frameworks.

- Ensuring compliance with international certification standards, such as ISO 26262 (automotive), DO-178C (aerospace), and IEC 61508 (industrial).

The Concept

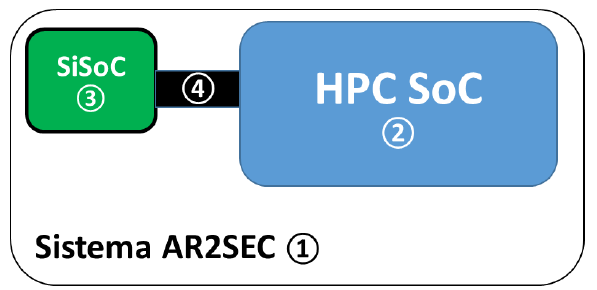

At the heart of AR2SEC is the SISoC (Safety Island System-on-Chip) — a specialized, fault-tolerant computing core designed to handle the most critical functions in a system.

This SISoC can be:

- Used independently in applications where ultra-reliability is essential.

- Paired with a High-Performance SoC (HPC SoC) to delegate less critical, compute-intensive tasks.

The SISoC and HPC SoC communicate through well-defined interfaces, enabling a clear separation of safety-critical and general-purpose computing. This modular design simplifies certification and increases adaptability across industries.

Technical Innovation

The AR2SEC architecture is built on five key innovation pillars:

1. Open Hardware & RISC-V ISA

Leveraging open-source technologies ensures greater transparency, adaptability and independence from non-European vendors.

2. Real-Time, Fault-Tolerant Performance

The platform supports complex real-time workloads — such as sensor fusion, obstacle detection and autonomous control — with guaranteed timing and reliability.

3. Mixed-Criticality System Design

Applications of different safety levels can coexist on the same platform, isolated through hardware-enforced mechanisms.

4. Modular, Configurable Design

The system can be customized for each industry or application, reducing time-to-market and cost.

5. Software Ecosystem Co-Designed with Hardware

From system software to validation and testing tools, AR2SEC provides a complete stack to ease development and certification.

MIG-20231014 project subsidized by CDTI (Centro de Desarrollo Tecnológico y la Innovación) and supported by the Ministry of Science and Innovation, approved in the call for the “Science and Innovation Missions” program linked to the PERTE of microelectronics and semiconductors of the year 2023 – Recovery, Transformation and Resilience Plan – Funded by the European Union – NextGenerationEU.